AI人工智慧专用处理器,IBM Power9大解析~

2018.07.27

"科技的进步已经远远超出人类的使用需求,像是IBM推出的Power9处理器,其眼光已经放在未来AI人工智慧上的学习,本篇文章将介绍IBM Power 9这颗强大处理器,其详细的规格解析适合对处理器有一定基础的技术高手参考,也欢迎有兴趣的朋友来吸收新知~"

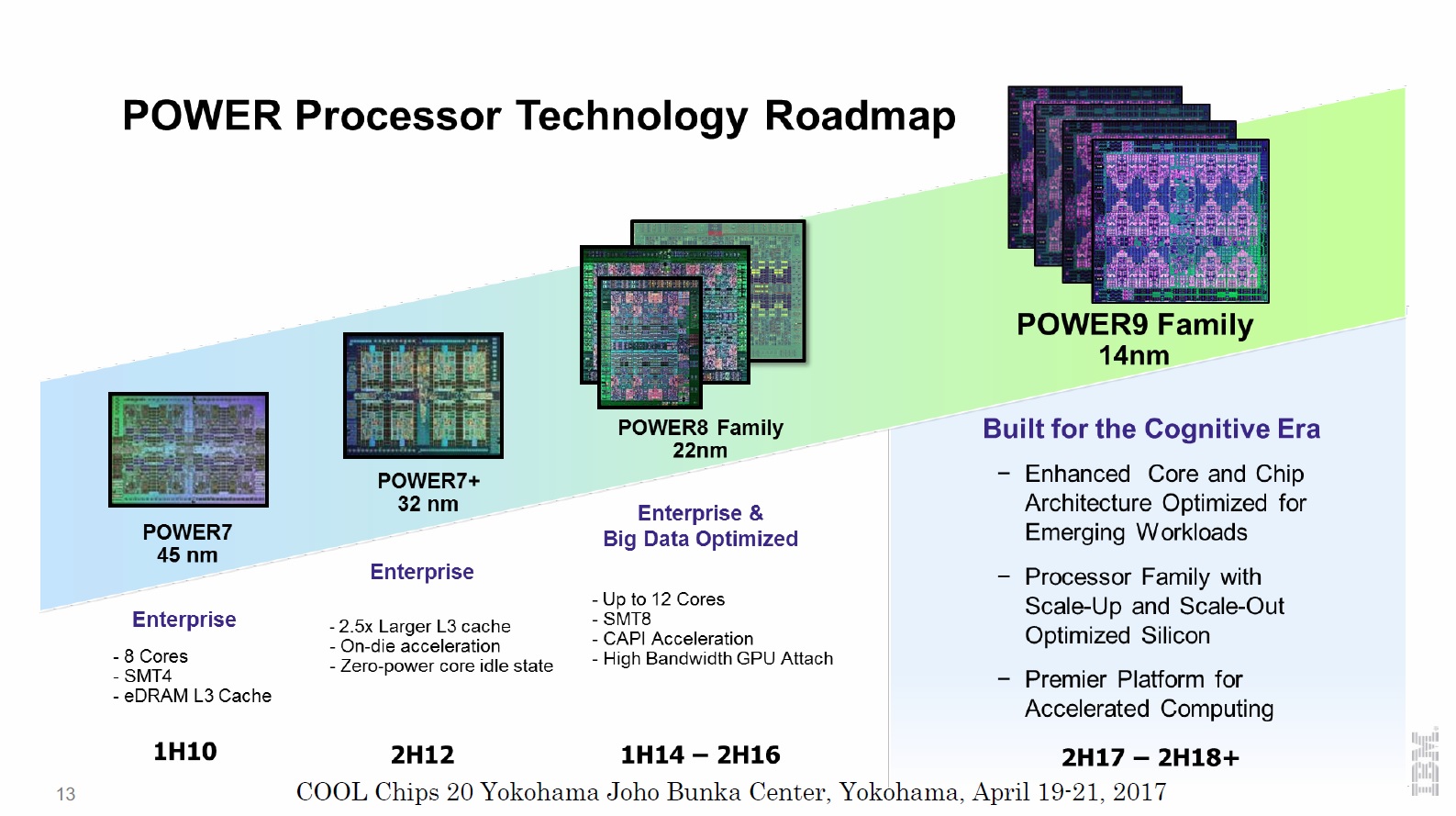

长期关心处理器技术发展的科科们,或多或少都曾听闻每年有两场IEEE(电机电子工程师学会)赞助的论坛:介绍「高效能处理器」的Hot Chips与「高效能省电处理器」的COOL Chips,也是众多厂商趁机进行技术行销的好场合。

刚好今年IBM分别在这两场活动,公开了其位处计算机工业技术顶点的两款旗舰处理器:

- COOL Chips 20:发祥于1974年古老RISC之一的IBM 810计画、高效能RISC伺服器的POWER9。

- Hot Chips 29:源自于1964年S/360大型CISC主机(Mainframe)的z14。

所以我们先来瞧瞧富有传奇色彩的POWER家族最新成员,由内而外,一层一层的抽丝剥茧。基本上,这种规格如同上帝、单价以一万美金为单位的超级旗舰处理器,看到先跪下就对了。

所以我们先来瞧瞧富有传奇色彩的POWER家族最新成员,由内而外,一层一层的抽丝剥茧。基本上,这种规格如同上帝、单价以一万美金为单位的超级旗舰处理器,看到先跪下就对了。

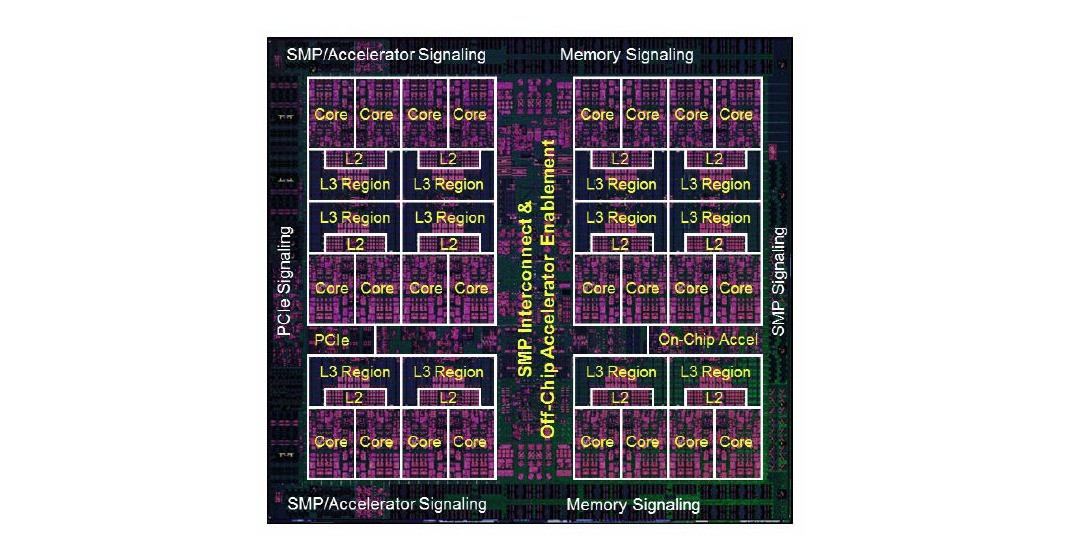

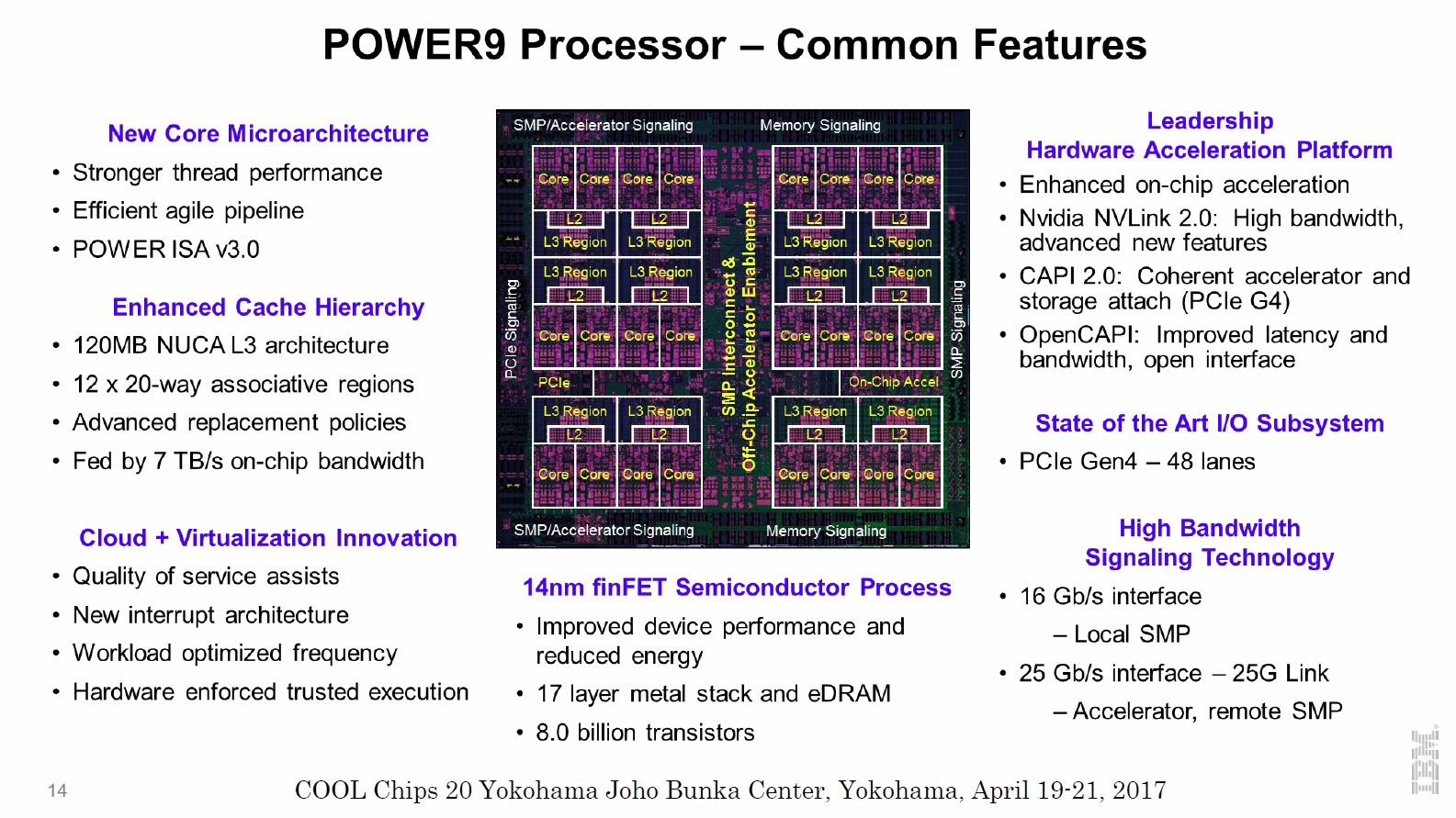

IBM POWER9规格概要

- 最多24核心/96同时执行绪。

- 最高时脉4GHz。

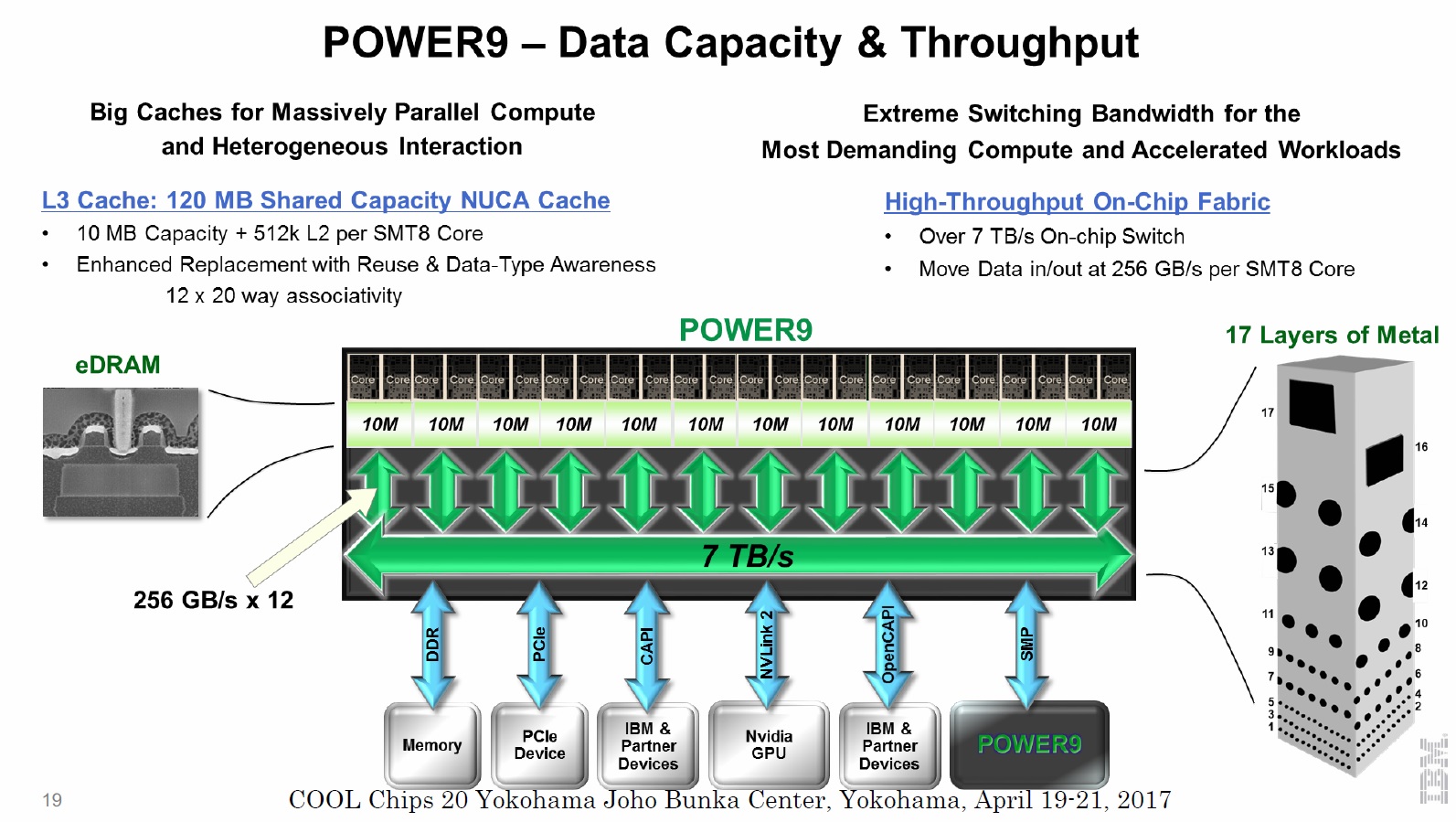

- Global Foundry 14nm FinFET制程,SOI晶圆,17层金属布线。

- 80亿电晶体,晶粒面积695平方公厘。

- Powe指令集架构3.0版。

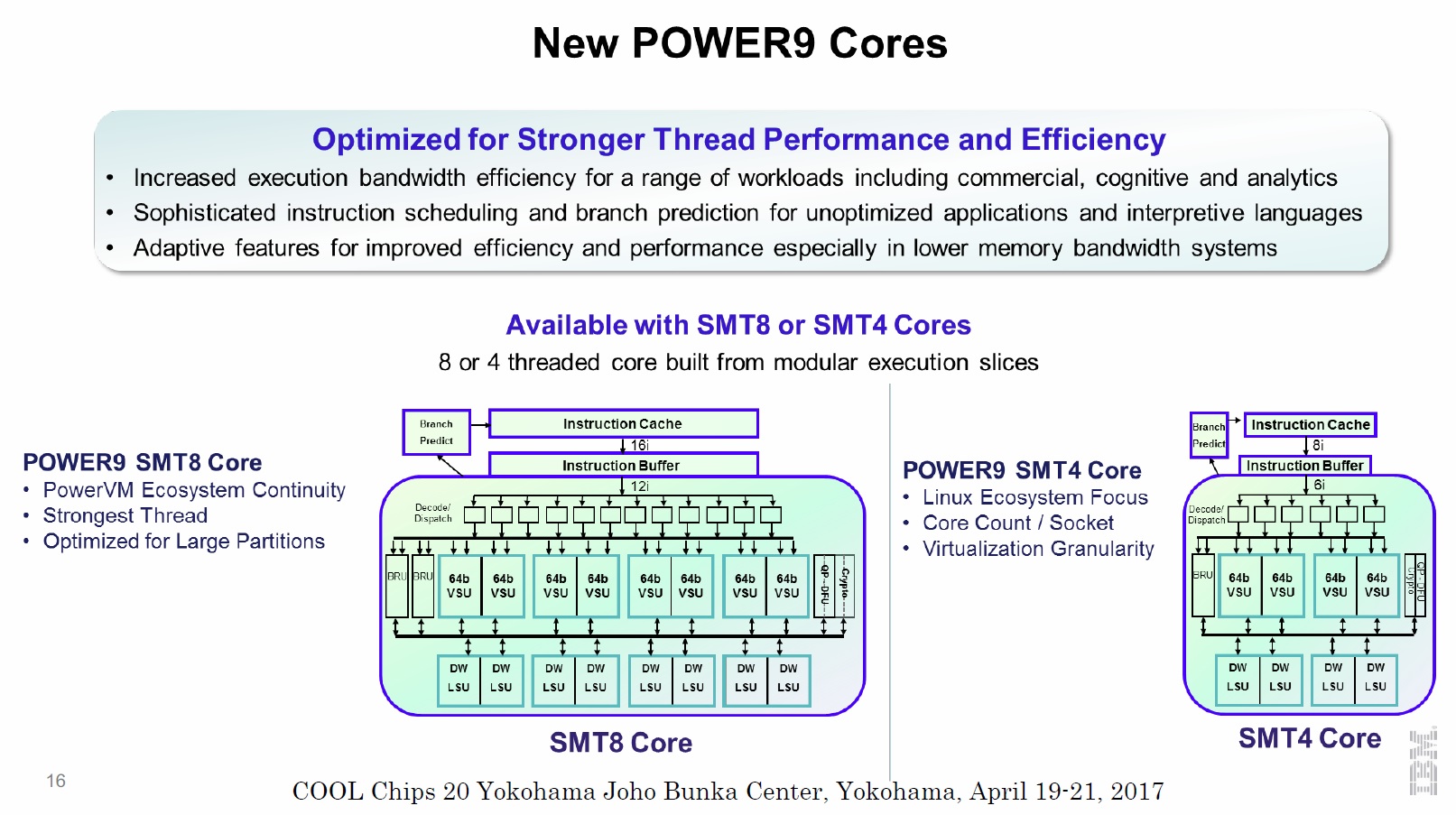

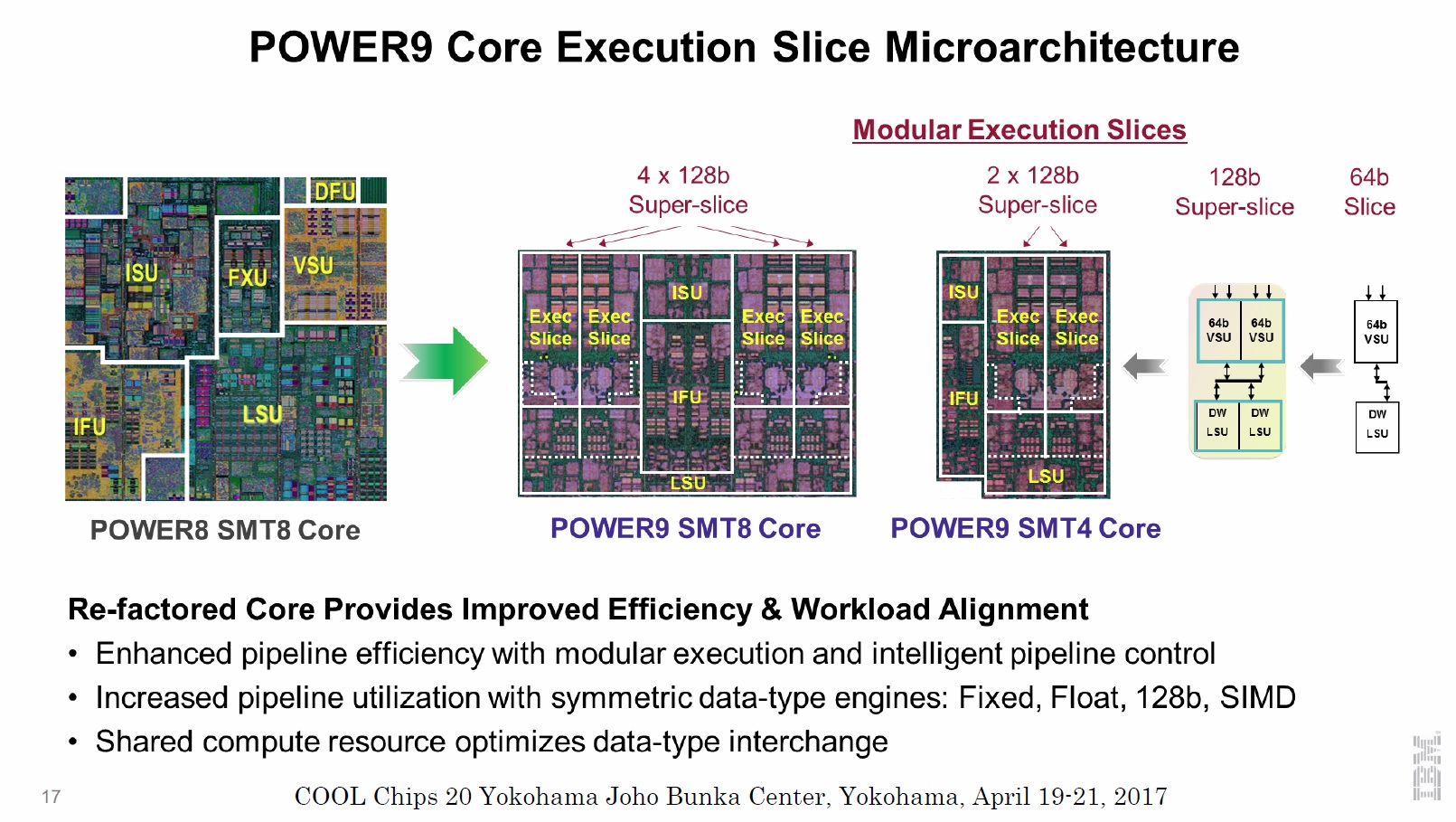

模组化的处理器核心

- 指令管线前端与执行单元完全独立。

- 一个独立的64位元单执行绪单元:Slice。

- 两个Slice组成一个128位元的Super-Slice。

- 可同时执行4个64位元纯量、或2个128位元向量运算。

- 可同时进行4个记忆体载入或回存。

- 接着就衍生出两种因应不同运算需求的处理器核心:

- 针对Linux环境追求虚拟化精细度的SMT4核心。

- 2组Super-Slice。

- 4条同时多执行绪(SMT)。

- 6个指令解码器。

- 最多24核心,96执行绪。 (不过目前仅贩售最多22核心的系统,可能是部份核心损坏的良率问题)

- 32kB L1指令快取,32kB L2资料快取。

- 256kB L2快取记忆体。

- 配合现有PowerVM虚拟化分割区的SMT8核心。

- 4组Super-Slice。

- 8条同时多执行绪(SMT)。

- 12个指令解码器。

- 最多12核心,96执行绪。

- 两块32kB L1指令快取,两块32kB L1资料快取。

- 512kB L2快取记忆体。

- 针对Linux环境追求虚拟化精细度的SMT4核心。

大型化的eDRAM快取记忆体

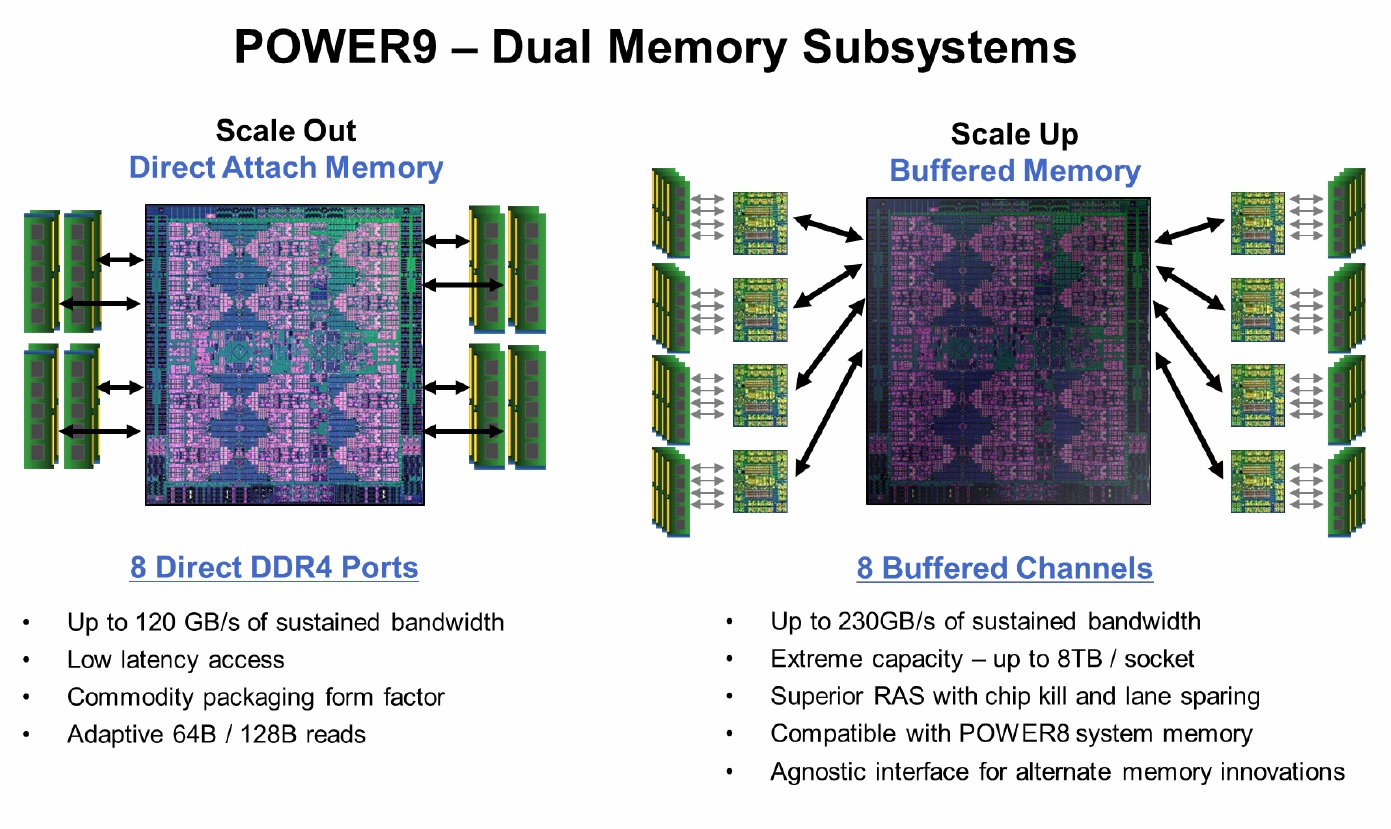

2种不同的主记忆体配置

- 拼系统数量与较低记忆体存取延迟的Scale Out(双处理器环境):8通道DDR4直连处理器,最高容量4TB,理论传输频宽120GB/s。

- 冲单一系统规模与记忆体损耗备援的Scale Up(多处理器环境):外接8颗记忆体缓冲晶片(Memory Buffer),最高容量8TB,理论传输频宽230GB/s,这组态可以提供加倍的25G Bluelink(后面会提到)。

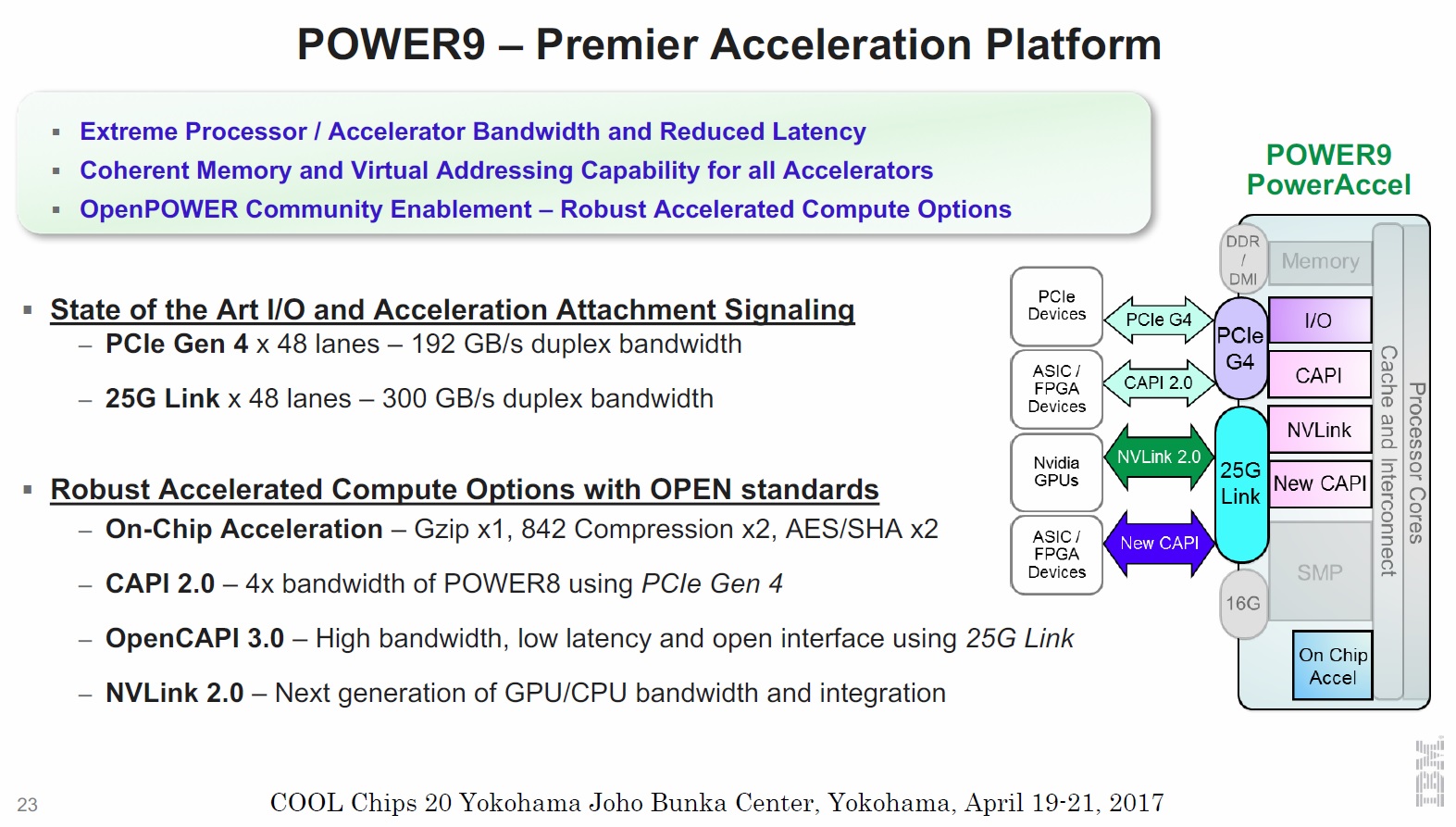

多样化的「外挂」介面

- 48 Lane PCIe Gen4:192GB理论双向频宽。

- 连接一般的PCIe装置。

- CAPI 2.0,提供POWER8的四倍效率。

- 48 Lane 25G Bluelink:300GB理论双向频宽。

- NVLink 2.0,前一版的两倍。

- OpenCAPI 3.0(或称为New CAPI):理论频宽高达200GB/s,预留连结加速器、储存设备或网路。

无愧地球上最强大泛用处理器的宝座